इलेक्ट्रिक कॅपेसिटन्स ही इलेक्ट्रोस्टॅटिक्सच्या मूलभूत संकल्पनांपैकी एक आहे. हा शब्द इलेक्ट्रिक चार्ज जमा करण्याच्या क्षमतेचा संदर्भ देतो. आपण वेगळ्या कंडक्टरच्या क्षमतेबद्दल बोलू शकता, आपण दोन किंवा अधिक कंडक्टरच्या प्रणालीच्या क्षमतेबद्दल बोलू शकता. शारीरिक प्रक्रिया समान आहेत.

सामग्री

विद्युत क्षमतेशी संबंधित मूलभूत संकल्पना

जर कंडक्टरला चार्ज q मिळाला असेल, तर त्यावर संभाव्य φ उद्भवतो. ही क्षमता भूमिती आणि वातावरणावर अवलंबून असते - भिन्न कंडक्टर आणि परिस्थितींसाठी, समान शुल्क भिन्न क्षमता निर्माण करेल. पण φ नेहमी q च्या प्रमाणात असते:

φ=Cq

गुणांक C ला इलेक्ट्रिकल कॅपेसिटन्स म्हणतात.जर आपण अनेक कंडक्टरच्या प्रणालीबद्दल बोलत आहोत (सामान्यतः दोन), तर जेव्हा एका कंडक्टरला (प्लेट) चार्ज दिला जातो तेव्हा संभाव्य फरक किंवा व्होल्टेज U उद्भवते:

U=Cq, म्हणून С=U/q

कॅपॅसिटन्सची व्याख्या संभाव्य फरक आणि चार्जच्या संभाव्य फरकाचे गुणोत्तर म्हणून केली जाऊ शकते. कॅपॅसिटन्ससाठी एसआय युनिट फॅराड आहे (ते फॅराड म्हणायचे). 1 F \u003d 1 V / 1 C. दुसऱ्या शब्दांत, प्रणालीची क्षमता 1 फॅराड असते, ज्यामध्ये 1 कूलॉम्ब चार्ज दिल्यावर 1 व्होल्टचा संभाव्य फरक निर्माण होतो. 1 फॅरड हे खूप मोठे मूल्य आहे. सराव मध्ये, अपूर्णांक मूल्ये बहुतेकदा वापरली जातात - पिकोफॅरॅड, नॅनोफॅरॅड, मायक्रोफॅराड.

सराव मध्ये, अशा कनेक्शनमुळे बॅटरी मिळविणे शक्य होते जे एका सेलच्या तुलनेत डायलेक्ट्रिकच्या मोठ्या ब्रेकडाउन व्होल्टेजचा सामना करू शकते.

कॅपेसिटरच्या कॅपेसिटन्सची गणना

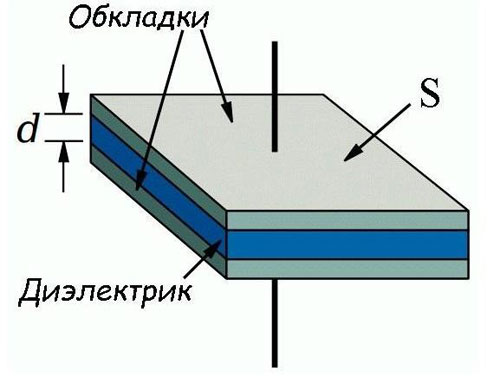

सराव मध्ये, सामान्यीकृत इलेक्ट्रिक कॅपेसिटन्ससह घटक म्हणून, बहुतेकदा वापरले जाते कॅपेसिटर, दोन सपाट कंडक्टर (प्लेट्स), डायलेक्ट्रिकद्वारे विभक्त केलेले. अशा कॅपेसिटरच्या इलेक्ट्रिक कॅपेसिटन्सची गणना करण्याचे सूत्र असे दिसते:

C=(S/d)*ε*ε0

कुठे:

- सी - क्षमता, एफ;

- S हे दर्शनी भागाचे क्षेत्रफळ आहे, sq.m;

- d हे प्लेट्समधील अंतर आहे, m;

- ε0 - विद्युत स्थिरांक, स्थिरांक, 8.854 * 10−12 f/m;

- ε ही डायलेक्ट्रिकची इलेक्ट्रिकल परमिटिव्हिटी आहे, एक आकारहीन परिमाण.

यावरून हे समजणे सोपे आहे की कॅपेसिटन्स प्लेट्सच्या क्षेत्रफळाच्या थेट प्रमाणात आणि कंडक्टरमधील अंतराच्या व्यस्त प्रमाणात आहे. तसेच, प्लेट्स वेगळे करणाऱ्या सामग्रीमुळे क्षमता प्रभावित होते.

कॅपॅसिटन्स निर्धारित करणार्या परिमाणांचा कॅपेसिटरच्या चार्ज साठवण्याच्या क्षमतेवर कसा परिणाम होतो हे समजून घेण्यासाठी, तुम्ही सर्वात मोठ्या संभाव्य कॅपेसिटन्ससह कॅपेसिटर तयार करण्यासाठी एक विचारप्रयोग करू शकता.

- तुम्ही प्लेट्सचे क्षेत्रफळ वाढवण्याचा प्रयत्न करू शकता. यामुळे उपकरणाच्या आकारमानात आणि वजनात तीव्र वाढ होईल. डायलेक्ट्रिकसह अस्तरांचा आकार कमी करण्यासाठी, ते गुंडाळले जातात (ट्यूबमध्ये, सपाट ब्रिकेट इ.).

- दुसरा मार्ग म्हणजे प्लेट्समधील अंतर कमी करणे. कंडक्टरला अगदी जवळ ठेवणे नेहमीच शक्य नसते, कारण डायलेक्ट्रिक लेयरने प्लेट्समधील विशिष्ट संभाव्य फरकाचा सामना केला पाहिजे. जाडी जितकी लहान असेल तितकी इन्सुलेटिंग गॅपची डायलेक्ट्रिक ताकद कमी होईल. आपण हा मार्ग घेतल्यास, अशी वेळ येईल जेव्हा अशा कॅपेसिटरचा व्यावहारिक वापर अर्थहीन होईल - ते केवळ अत्यंत कमी व्होल्टेजवर कार्य करू शकते.

- डायलेक्ट्रिकची विद्युत पारगम्यता वाढवणे. हा मार्ग सध्या अस्तित्वात असलेल्या उत्पादन तंत्रज्ञानाच्या विकासावर अवलंबून आहे. इन्सुलेटिंग सामग्रीमध्ये केवळ उच्च पारगम्यता मूल्यच नाही तर चांगले डायलेक्ट्रिक गुणधर्म देखील असले पाहिजेत आणि आवश्यक वारंवारता श्रेणीमध्ये त्याचे पॅरामीटर्स देखील राखले पाहिजेत (कॅपॅसिटर ज्या वारंवारतेवर चालते त्या वाढीसह, डायलेक्ट्रिकची वैशिष्ट्ये कमी होतात).

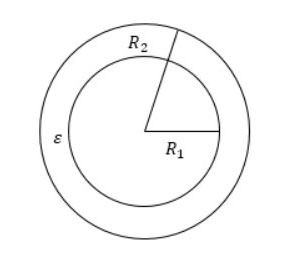

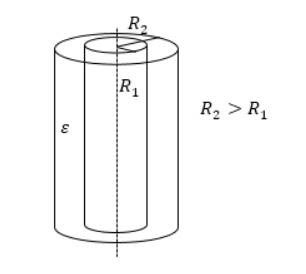

काही विशेष किंवा संशोधन प्रतिष्ठापनांमध्ये गोलाकार किंवा दंडगोलाकार कॅपेसिटर वापरता येतात.

गोलाकार कॅपेसिटरची क्षमता सूत्राद्वारे मोजली जाऊ शकते

C=4*π*ε*ε0 *R1R2/(R2-R1)

जेथे R ही गोलांची त्रिज्या आहे आणि π=3.14.

दंडगोलाकार कॅपेसिटरसाठी, कॅपेसिटन्सची गणना खालीलप्रमाणे केली जाते:

C=2*π*ε*ε0 *l/ln(R2/R1)

l ही सिलेंडरची उंची आहे आणि R1 आणि R2 त्यांची त्रिज्या आहेत.

मूलभूतपणे, दोन्ही सूत्रे फ्लॅट कॅपेसिटरच्या सूत्रापेक्षा भिन्न नाहीत. कॅपेसिटन्स नेहमी प्लेट्सच्या रेखीय परिमाण, त्यांच्यामधील अंतर आणि डायलेक्ट्रिकच्या गुणधर्मांद्वारे निर्धारित केले जाते.

कॅपेसिटरची मालिका आणि समांतर कनेक्शन

कॅपेसिटर कनेक्ट केले जाऊ शकतात मालिकेत किंवा समांतर, नवीन वैशिष्ट्यांसह संच प्राप्त करणे.

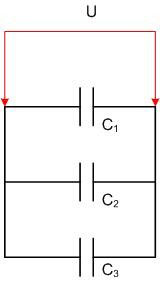

समांतर कनेक्शन

जर तुम्ही कॅपेसिटरला समांतर कनेक्ट केले तर परिणामी बॅटरीची एकूण क्षमता त्याच्या घटकांच्या सर्व क्षमतेच्या बेरजेइतकी असेल. जर बॅटरीमध्ये समान डिझाइनचे कॅपेसिटर असतील तर, हे प्लेट्सच्या क्षेत्रफळाची जोड म्हणून मानले जाऊ शकते. या प्रकरणात, बॅटरीच्या प्रत्येक सेलवरील व्होल्टेज समान असेल आणि शुल्क वाढेल. समांतर जोडलेल्या तीन कॅपेसिटरसाठी:

- U=U1=यू2=यू3;

- q=q1+q2+q3;

- C=C1+C2+C3.

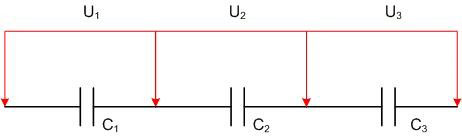

सीरियल कनेक्शन

मालिकेत कनेक्ट केल्यावर, प्रत्येक कॅपेसिटन्सचे शुल्क समान असेल:

q1=q2=q3=q

एकूण व्होल्टेज आनुपातिकपणे वितरीत केले जाते कॅपेसिटरची क्षमता:

- यू1=q/C1;

- यू2=q/C2;

- यू3= q/C3.

जर सर्व कॅपेसिटर समान असतील, तर प्रत्येकामध्ये समान व्होल्टेज कमी होईल. एकूण क्षमता खालीलप्रमाणे आढळते:

С=q/( U1+U2+U3), म्हणून 1/С=( U1+U2+U3)/q=1/C1+1/एस2+1/एस3.

तंत्रज्ञानामध्ये कॅपेसिटरचा वापर

विद्युत ऊर्जा साठवण उपकरणे म्हणून कॅपेसिटर वापरणे तर्कसंगत आहे. या क्षमतेमध्ये, ते लहान संचयित ऊर्जेमुळे इलेक्ट्रोकेमिकल स्त्रोतांशी (गॅल्व्हॅनिक बॅटरी, कॅपेसिटर) स्पर्धा करू शकत नाहीत आणि डायलेक्ट्रिकमधून चार्ज गळतीमुळे जलद स्व-डिस्चार्ज होऊ शकतात.परंतु दीर्घ कालावधीसाठी ऊर्जा जमा करण्याची आणि नंतर जवळजवळ त्वरित ती देण्याची त्यांची क्षमता मोठ्या प्रमाणात वापरली जाते. हा गुणधर्म फोटोग्राफीसाठी फ्लॅश दिवे किंवा लेसरच्या उत्तेजनासाठी दिवे वापरला जातो.

रेडिओ अभियांत्रिकी आणि इलेक्ट्रॉनिक्समध्ये कॅपेसिटरचा मोठ्या प्रमाणावर वापर केला जातो. सर्किट्सच्या फ्रिक्वेंसी-सेटिंग घटकांपैकी एक म्हणून रेझोनंट सर्किट्सचा भाग म्हणून कॅपेसिटन्सचा वापर केला जातो (दुसरा घटक इंडक्टन्स आहे). हे व्हेरिएबल घटकास विलंब न करता थेट प्रवाह पास न करण्याच्या कॅपेसिटरची क्षमता देखील वापरते. एका स्टेजच्या डीसी मोडचा दुसऱ्या स्टेजवरील प्रभाव वगळण्यासाठी अॅम्प्लीफायिंग स्टेज वेगळे करण्यासाठी असा अॅप्लिकेशन सामान्य आहे. मोठ्या कॅपेसिटरचा वापर वीज पुरवठ्यामध्ये स्मूथिंग फिल्टर म्हणून केला जातो. कॅपेसिटरचे इतर अनुप्रयोग देखील मोठ्या संख्येने आहेत जेथे त्यांचे गुणधर्म उपयुक्त आहेत.

काही व्यावहारिक कॅपेसिटर डिझाइन

सराव मध्ये, फ्लॅट कॅपेसिटरच्या विविध डिझाइनचा वापर केला जातो. डिव्हाइसची रचना त्याची वैशिष्ट्ये आणि व्याप्ती निर्धारित करते.

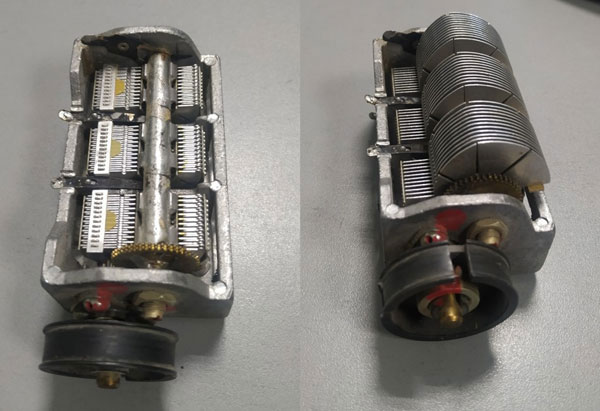

व्हेरिएबल कॅपेसिटर

व्हेरिएबल कॅपेसिटरचा एक सामान्य प्रकार (व्हीपीसी) मध्ये हवेने विभक्त केलेल्या जंगम आणि स्थिर प्लेट्सचा ब्लॉक किंवा घन इन्सुलेटर असतो. जंगम प्लेट्स अक्षाभोवती फिरतात, ओव्हरलॅप क्षेत्र वाढवतात किंवा कमी करतात. जेव्हा मूव्हिंग ब्लॉक काढला जातो तेव्हा इंटरइलेक्ट्रोड अंतर अपरिवर्तित राहतो, परंतु प्लेट्समधील सरासरी अंतर देखील वाढते. इन्सुलेटरचा डायलेक्ट्रिक स्थिरांक देखील अपरिवर्तित राहतो. प्लेट्सचे क्षेत्रफळ आणि त्यांच्यामधील सरासरी अंतर बदलून क्षमता नियंत्रित केली जाते.

ऑक्साईड कॅपेसिटर

पूर्वी, अशा कॅपेसिटरला इलेक्ट्रोलाइटिक म्हणतात. यात इलेक्ट्रोलाइटने गर्भित केलेल्या कागदाच्या डायलेक्ट्रिकद्वारे विभक्त केलेल्या फॉइलच्या दोन पट्ट्या असतात. पहिली पट्टी एक प्लेट म्हणून काम करते, दुसरी प्लेट इलेक्ट्रोलाइट म्हणून काम करते. डायलेक्ट्रिक हा धातूच्या एका पट्टीवर ऑक्साईडचा पातळ थर असतो आणि दुसरी पट्टी वर्तमान संग्राहक म्हणून काम करते.

ऑक्साईडचा थर खूप पातळ आहे आणि इलेक्ट्रोलाइट त्याला जवळ करतो या वस्तुस्थितीमुळे, मध्यम आकारासह पुरेशी मोठी क्षमता प्राप्त करणे शक्य झाले. याची किंमत कमी ऑपरेटिंग व्होल्टेज होती - ऑक्साईड लेयरमध्ये उच्च विद्युत शक्ती नसते. ऑपरेटिंग व्होल्टेजच्या वाढीसह, कॅपेसिटरच्या परिमाणांमध्ये लक्षणीय वाढ करणे आवश्यक आहे.

दुसरी समस्या अशी आहे की ऑक्साईडमध्ये एकतर्फी चालकता आहे, म्हणून अशा कंटेनरचा वापर केवळ ध्रुवीयतेसह डीसी सर्किटमध्ये केला जातो.

आयनिस्टर

वर दर्शविल्याप्रमाणे, वाढीच्या पारंपारिक पद्धती कॅपेसिटर नैसर्गिक मर्यादा आहेत. म्हणूनच, वास्तविक यश म्हणजे आयनिस्टर्सची निर्मिती.

जरी हे उपकरण कॅपेसिटर आणि बॅटरीमधील मध्यवर्ती दुवा मानले जात असले तरी, थोडक्यात ते अद्याप एक कॅपेसिटर आहे.

दुहेरी इलेक्ट्रिकल लेयरच्या वापरामुळे प्लेट्समधील अंतर खूपच कमी झाले आहे. प्लेट्स विरुद्ध शुल्कासह आयनांचे स्तर आहेत. फोम केलेल्या सच्छिद्र सामग्रीमुळे प्लेट्सचे क्षेत्र झपाट्याने वाढवणे शक्य झाले. परिणामी, शेकडो फॅराड्सच्या क्षमतेसह सुपरकॅपेसिटर मिळवणे शक्य आहे.अशा उपकरणांचा एक जन्मजात रोग म्हणजे कमी ऑपरेटिंग व्होल्टेज (सामान्यतः 10 व्होल्ट्सच्या आत).

तंत्रज्ञानाचा विकास स्थिर राहत नाही - बर्याच भागातील दिवे द्विध्रुवीय ट्रान्झिस्टरद्वारे विस्थापित केले जातात, त्या बदल्यात, एकध्रुवीय ट्रायोड्सद्वारे बदलले जातात. सर्किट्स डिझाइन करताना, ते शक्य असेल तेथे इंडक्टन्सपासून मुक्त होण्याचा प्रयत्न करतात. आणि कॅपेसिटरने दुसर्या शतकासाठी त्यांची स्थिती गमावली नाही, लेडेन जारच्या शोधापासून त्यांची रचना मूलभूतपणे बदललेली नाही आणि त्यांची कारकीर्द संपण्याची कोणतीही शक्यता नाही.

तत्सम लेख: